l’Emetteur Récepteur Cyclique (l’ERC )

Le présent article décrit les principes et présente globalement les spécifications de l’ERC (Emetteur Récepteur Cyclique) équipement central de la chaîne Informations Codées.

Principes généraux :

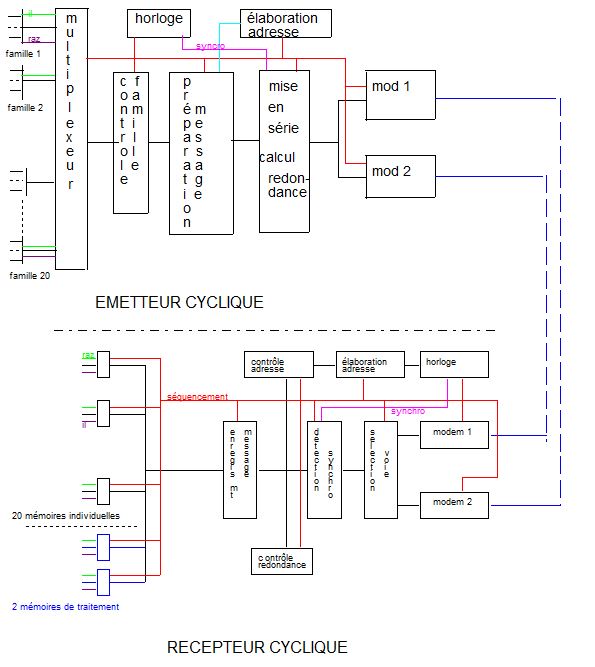

L’Emetteur Récepteur Cyclique est chargé de l’acquisition, de la transmission et de la restitution des informations. Son cycle est de 10 secondes, et sa capacité est de 20 familles d’informations.

Une famille représente

• Soit une mesure codée sur 8 bits (7 bits de valeur et 1 bit de signe)

• Soit 8 positions de signalisations.

Compte tenu des supports de transmission de l’époque la vitesse de transmission a été fixée à 50 bits par seconde. Les canaux de transmission espacés de 120 Hertz se situent dans la bande supra-phonique entre 2340 hertz et 2940hertz. La modulation est du type à déplacement de fréquence.

Acquisition :

Chaque information et sa valeur complémentaire sont fournies par les équipements de codage en parallèle. La sécurité de lecture se faisant à l’aide de signaux de validation : IL (interdiction de lecture) et RAZ (remise à zéro après lecture).

Traitement et Transmission :

L’ERC établit la validité des informations reçues et crée une trame comportant 4 bits de synchro du message, 5 bits d’adresse (pour identifier la famille concernée), les 8 bits d’informations, 1 bit de validité (image de la validité du départ), 4 bits de redondance (pour la sécurisation de la transmission).

En 10 secondes l’E.R.C. fait transiter, outre les 20 trames porteuses d’informations, deux trames supplémentaires permettant l’auto test de l’appareil.

L’E.R.C. envoie le même message sur deux voies différentes aussi indépendantes que possible (exemple : CPL et liaisons France Télécom)

Réception et restitution :

L’E.R.C. choisit arbitrairement une des deux voies de transmission (sauf si une d’entre elles présente un niveau de réception trop faible).

Il vérifie les messages reçus à l’aide des bits de redondance et met à disposition des équipements décodeurs, avec un processus d’autorisation de lecture, les informations et leurs compléments.

Le détail :

Acquisition :

Les informations fournies par les équipements de codage se présentent sous forme parallèle en direct et complément. Ainsi une mesure codée sur 8 bits par le C.C.D ou le C.A.N apparait à la sortie de ces équipements et donc à l’entrée de l’Emetteur sur 16 fils. Il en va de même pour une famille de signalisations fournie par le Codeur.

L’acquisition est séquencée et contrôlée par deux signaux :

• L’Interdiction de Lecture (I.L.) émis par l’équipement de codage vers l’émetteur cyclique. Ce signal, d’une durée de 10 ms, fourni en direct et complément, indique à l’émetteur que l’information (mesure ou famille de signalisations) n’est pas disponible sur les 16 fils de sortie (en cours de mise à jour).

• La Remise à Zéro (R.A.Z) est un signal de 1,5 ms émis en direct et complément par l’émetteur cyclique vers l’équipement de codage dès que la lecture est terminée.

Le signal d’I.L. encadre donc les mises à jour des mémoires de sortie des équipements de codage. Cette mise à jour a lieu 7 ms après le début du signal d’I.L pour permettre une lecture sûre si celle-ci a débutée juste avant la montée de ce signal.

Les informations et les signaux de séquencement sont fournis en direct et complément. Par vérification de cette complémentarité dans l’E.R.C. on réalise deux contrôles : premièrement on détecte les anomalies des mémoires de sortie et de la connectique, deuxièmement, en forçant volontairement une non-complémentarité sur un ou plusieurs bits l’équipement amont peut signaler une défaillance à l’équipement aval qui pourra ainsi la retransmettre.

Traitement et Transmission :

L’E.R.C, pour traiter et transmettre 20 familles en 10 s dispose donc de 500 ms par famille.

Chaque famille d’informations, repérée par son connecteur d’entrée est accompagnée, dans le message émis vers le récepteur, par une adresse (de 1 à 20), par un bit de validité élaboré par le contrôle de complémentarité (entre l’information et son complément en provenance du codeur), par un signal de synchronisation entre les familles afin que le récepteur se synchronise, enfin par un code de redondance en fin de message pour se prémunir des aléas de la transmission.

En conclusion le message émis pour transmettre une famille comprend dans l’ordre d’émission : 4 bits de synchro, 5 bits d’adresse, 8 bits d’informations, 1 bit de validité, 4 bits de redondance calculés sur adresse, information et validité. Les poids forts sont transmis en tête.

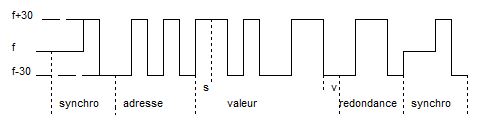

Le schéma ci-dessous illustre la trame émise

– v : est la validité/ invalidité de la valeur.F+30 Hz invalide, F-30Hz valide.

– Le signal de synchro est caractéristique dans la trame, ses deux moments à la fréquence F suivis d’un moment à F+30Hz et d’un moment à F-30Hz permettent de le détecter par le récepteur;

– Les poids forts des codes d’adresses et de valeurs sont transmis en tête. Un bit à 1 est transmis par la fréquence F+30 Hz et un bit à 0 par la fréquence F-30 Hz.

La trame se compose donc de 22 bits, à la vitesse de transmission de 50 bits par seconde sa durée de transmission est de 440ms.Pour 20 familles la durée de transmission est de 8,8 s. Pour respecter le cycle de 10s il reste 1,2 s qu’il faut neutraliser. Ce temps est utilisé pour transmettre deux familles supplémentaires appelées familles d’autocontrôle, d’adresses 21 et 22.Ces deux familles internes à l’E.R.C ont pour but de vérifier le bon fonctionnement des organes principaux de l’émetteur et du récepteur ainsi que la transmission. Ces deux familles élaborées par l’émetteur contiennent des codes valeur complémentaires qui associés à des adresses fixes donneront chacune un code de contrôle parfaitement déterminé. Il restera au récepteur à vérifier la cohérence de ces deux familles pour valider à priori ou invalider totalement le cycle de transmission suivant.

L’Emetteur et le Récepteur disposent chacun d’une horloge interne pilotée par quartz de précision 10-4 et des mêmes registres de comptage pour élaborer les différents signaux de séquencement.

Réception et Restitution :

L’Emetteur émet simultanément sur deux voies séparées qui empruntent, pour des raisons de sécurité, de disponibilité et de coût, des circuits différents le plus souvent un circuit FT et un circuit CPL. Le récepteur contrôle le niveau de réception sur les deux voies et se cale indifféremment sur l’une ou l’autre, sauf sur celle qui présente éventuellement un niveau insuffisant.

Le récepteur identifie le signal de synchro par ses deux moments consécutifs de fréquence F suivis d’une transition F+30Hz / F-30Hz : ceci constitue la synchro messages. Pour contrôler la validité de la transmission le récepteur élabore le code de redondance qu’il compare à celui reçu. Enfin le récepteur élabore un code d’adresse qu’il compare à celui reçu : s’il y a discordance il force son compteur interne avec l’adresse reçue de l’émetteur et l’incrémente au premier signal de synchro reçu. Ces trois dispositifs permettent de valider la transmission et de synchroniser le récepteur sur l’émetteur ainsi que les familles. Au démarrage le récepteur se met en attente des deux familles d’autocontrôle correctement reçues pour se déclarer prêt à recevoir les informations.

Le récepteur dispose de 20 mémoires individuelles (numérotées de1 à20) raccordées chacune à un connecteur de sortie et 2 mémoires de traitement permettant chacune un raccordement à un calculateur.

Le récepteur met à jour chaque mémoire individuelle toute les 10s, il aiguille, en fonction du code adresse, la valeur sur la mémoire individuelle correspondante. Cette information est présentée sur 16 fils en direct et complément, elle est encadrée au moment de son transfert par un signal d’interdiction de lecture utilisé par l’équipement aval.

Le récepteur présente chaque famille simultanément sur les deux mémoires de traitement toute les 440ms. Dans ce cas, outre la valeur, l’adresse est présente en direct et complément. Comme précédemment un signal interdiction de lecture encadrant le transfert dans ces mémoires est fourni vers les calculateurs, en retour ceux-ci renvoient un signal de remise à zéro lorsqu’ils ont lu l’information.

Les deux familles d’autocontrôle ne sont pas présentées sur les mémoires de traitement. Toutefois 15 ans après la mise en service des premiers E.R.C, le nouveau système répondant au Schéma Directeur d’Automatisation du Réseau du Transport a conduit le Département Automatisation des Réseaux à apporter une modification “hard” dans les récepteurs pour laisser passer ces deux familles sur les mémoires de traitement dans le but de réduire la connectique tout en préservant une bonne sécurité.

Les signaux I.L et R.A.Z sont également présentés en direct et complément et l’invalidité d’une information détectée à l’émetteur et transmise dans le message se traduit par le forçage d’une non complémentarité sur un bit valeur des mémoires de sortie.

En résumé, l’E.R.C est un équipement de transmission cyclique unidirectionnel, la structure des messages permettant au récepteur de se synchroniser sur l’émetteur. Aux interfaces, la validité des informations est contrôlée tant à l’acquisition qu’à la restitution par le mécanisme “ direct et complément». Le séquencement aux interfaces est piloté par deux signaux calibrés : l’I.L et la R.A.Z.

Le schéma ci-après illustre de façon sommaire les principes de fonctionnement de l’E.R.C.